半导体包装

发布时间:2025-08-01

关键词:半导体抗静电

点击量:728

在半导体器件从生产到应用的全生命周期中,包装容器是抵御静电威胁的第一道防线。随着芯片集成度不断提升,其对静电的敏感度呈指数级增长,抗静电包装容器已从简单的 “储物工具” 升级为具备精准防护功能的核心组件,直接影响半导体产品的良率与可靠性。

一、半导体抗静电包装容器的核心分类

根据应用场景与防护等级,主流容器可分为三大类:

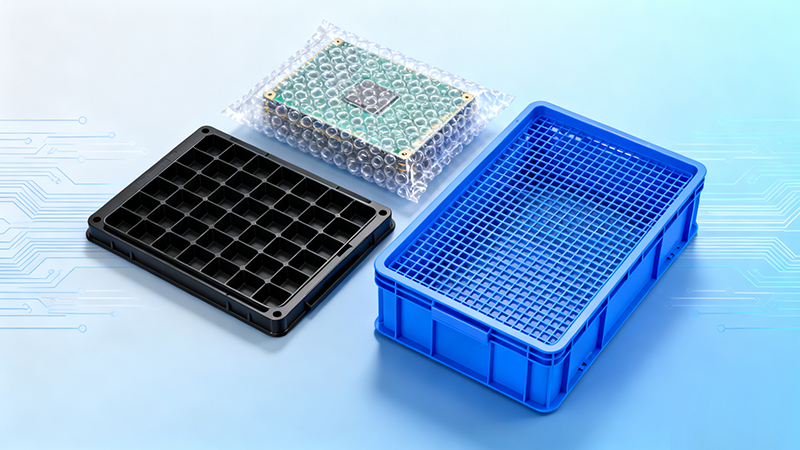

芯片级容器:以抗静电载带和芯片托盘为代表。载带采用防静电聚乙烯或导电聚苯乙烯制成,表面电阻控制在 10⁶-10¹¹Ω,配合导电盖带使用,可实现单颗芯片的独立封装,广泛用于 SMT 贴片工艺;芯片托盘则通过精密注塑成型,内部设有定位凹槽,防止芯片移位,同时底部预留接地触点,确保堆叠时静电可快速释放。

运输级容器:包括防静电周转箱与屏蔽运输盒。周转箱多采用添加碳纳米管的复合塑料,具备耐冲击、耐高低温特性,箱壁内置导电筋条,形成立体接地网络,可适配自动化仓储系统;屏蔽运输盒采用 “金属镀层 + 防静电内衬” 双层结构,屏蔽效能达 30dB 以上,能隔绝外部电磁干扰与静电场,适用于长途运输高敏感芯片。

存储级容器:主要为防静电真空包装罐与密封柜。真空包装罐通过抽真空隔绝空气与湿度,配合防静电密封圈,可长期存储晶圆等核心器件;密封柜则集成离子中和系统,实时消除内部静电,同时配备湿度传感器,将环境湿度稳定在 30%-50% 的安全范围。

二、容器设计的关键技术要求

静电控制性能:容器表面电阻需稳定在 10⁶-10¹²Ω 区间,避免因电阻过低产生漏电风险,或过高导致静电积累。部分高端容器还会在内部喷涂抗静电涂层,涂层厚度控制在 5-10μm,确保长期使用后性能不衰减。

结构稳定性:容器需通过跌落测试(1.2 米高度跌落至水泥地面)与振动测试(10-500Hz 正弦振动),确保在运输过程中不变形、不开裂。同时,内部结构需避免锐角设计,防止划伤芯片表面或产生静电尖端放电。

兼容性与适配性:容器尺寸需符合半导体行业标准(如 JEDEC 规范),例如晶圆托盘直径需适配 8 英寸、12 英寸晶圆尺寸;接口设计需兼容自动化设备,如周转箱侧边需预留机械臂抓取槽,提升生产效率。

三、应用场景的精准适配策略

在晶圆制造环节,需使用超高洁净度的抗静电容器,内壁粗糙度 Ra<0.8μm,避免粉尘吸附;在芯片测试环节,测试托盘需具备耐高温特性(可承受 125℃以上烘烤),满足测试过程中的温度需求;在国际运输环节,需选用具备 IP67 防护等级的屏蔽容器,同时配备 GPS 定位模块,实时监控运输状态,防止容器破损导致静电侵入。

四、质量管控与维护要点

半导体抗静电包装容器需建立全生命周期管理体系:新容器入库前需进行表面电阻测试与屏蔽效能检测,合格后方可投入使用;使用过程中,需每月清洁容器表面,避免油污、粉尘影响抗静电性能;报废前需进行性能评估,对于表面电阻超出标准范围的容器,需统一回收处理,防止二次污染。

作为半导体供应链中的关键一环,抗静电包装容器的技术升级与质量管控,是保障芯片安全、推动半导体产业高质量发展的重要基础。未来,随着柔性电子、量子芯片等新技术的涌现,容器将向 “智能化 + 多功能化” 方向发展,进一步提升防护精度与使用效率。